中國科學(xué)院研究生數(shù)字集成電路設(shè)計講義 集成電路設(shè)計的核心要素與實踐

數(shù)字集成電路設(shè)計是現(xiàn)代微電子技術(shù)的基石,中國科學(xué)院研究生階段的數(shù)字集成電路設(shè)計講義系統(tǒng)性地闡述了從理論到實踐的全過程。本文將基于講義的核心內(nèi)容,概述集成電路設(shè)計的關(guān)鍵環(huán)節(jié)、技術(shù)挑戰(zhàn)與發(fā)展趨勢。

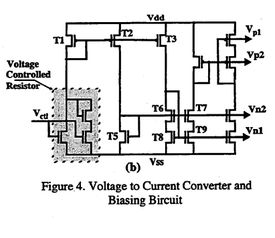

集成電路設(shè)計始于系統(tǒng)級設(shè)計,明確芯片的功能、性能指標與功耗預(yù)算。設(shè)計者需進行高層次建模與仿真,利用硬件描述語言(如Verilog或VHDL)描述電路行為,這是將抽象概念轉(zhuǎn)化為可操作設(shè)計的第一步。中國科學(xué)院的研究生課程強調(diào)這一階段的創(chuàng)新思維與系統(tǒng)優(yōu)化能力,培養(yǎng)學(xué)生在復(fù)雜約束下進行架構(gòu)探索的能力。

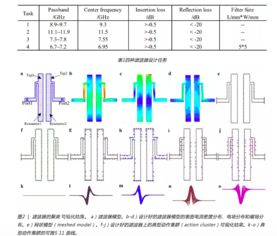

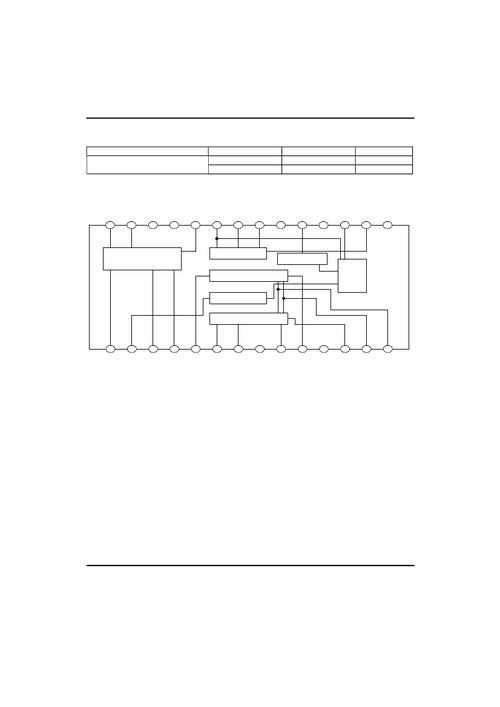

邏輯綜合與驗證是設(shè)計的核心環(huán)節(jié)。綜合工具將行為級描述轉(zhuǎn)換為門級網(wǎng)表,優(yōu)化面積、時序和功耗。中國科學(xué)院講義詳細講解了靜態(tài)時序分析、形式驗證與測試向量生成,確保設(shè)計在邏輯功能與時序約束上的正確性。研究生通過實驗掌握EDA工具的使用,理解算法背后的物理意義,這是銜接理論與工藝的關(guān)鍵。

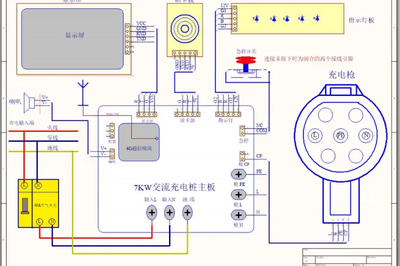

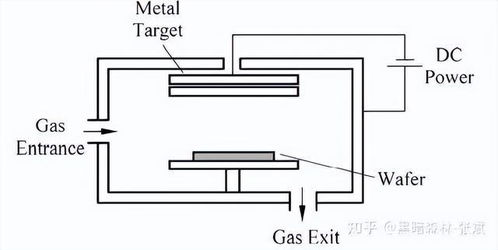

物理設(shè)計涉及布局布線,將邏輯網(wǎng)表映射到實際硅片。講義涵蓋版圖設(shè)計、時鐘樹綜合、電源規(guī)劃等專題,突出納米級工藝下的互連線效應(yīng)、信號完整性與功耗管理。中國科學(xué)院在先進工藝節(jié)點研究方面具有深厚積累,課程結(jié)合實例分析如時序收斂、設(shè)計規(guī)則檢查等實戰(zhàn)問題,培養(yǎng)學(xué)生的工程實現(xiàn)能力。

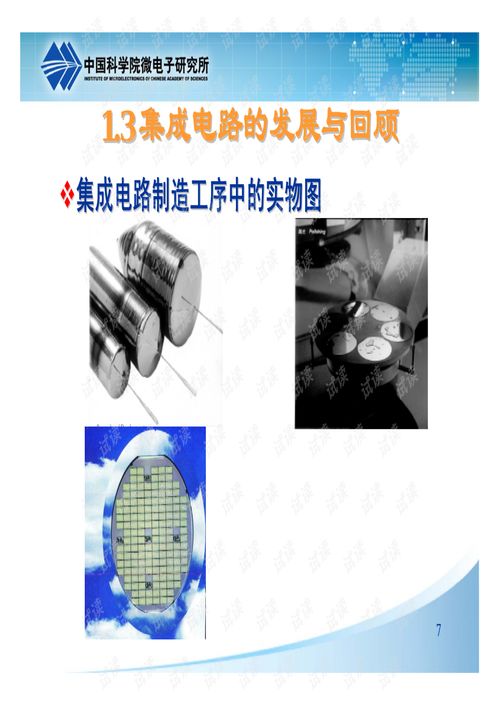

設(shè)計流程的終點是流片與測試。講義介紹芯片制造后的測試策略、可測試性設(shè)計(DFT)與可靠性評估。中國科學(xué)院注重產(chǎn)學(xué)研結(jié)合,許多研究課題面向?qū)嶋H應(yīng)用,如人工智能加速器、通信芯片等,使學(xué)生體驗從設(shè)計到產(chǎn)品的完整鏈條。

集成電路設(shè)計面臨摩爾定律放緩后的新挑戰(zhàn)。中國科學(xué)院講義前瞻性地探討了異構(gòu)集成、近似計算、開源EDA等方向,鼓勵研究生探索新材料、新架構(gòu)下的設(shè)計方法學(xué)。通過這門課程,學(xué)生不僅掌握技術(shù)細節(jié),更培養(yǎng)解決前沿問題的創(chuàng)新能力,為中國集成電路產(chǎn)業(yè)的自主發(fā)展儲備高端人才。

中國科學(xué)院研究生數(shù)字集成電路設(shè)計講義是一套融合基礎(chǔ)理論與工程實踐的權(quán)威指南,它系統(tǒng)化地構(gòu)建了學(xué)生的知識體系,并激發(fā)他們在這一關(guān)鍵領(lǐng)域的探索熱情。

如若轉(zhuǎn)載,請注明出處:http://m.wqulapa.cn/product/60.html

更新時間:2026-04-12 18:57:08